五、STM32——时钟

1 什么是时钟

时钟是单片机运行的基础,时钟信号推动单片机内各个部分执行相应的指令。时钟系统就是CPU的脉搏,决定cpu速率,像人的心跳一样 只有有了心跳,人才能做其他的事情,而单片机有了时钟,才能够运行执行指令,才能够做其他的处理 (点灯,串口,ADC),时钟的重要性不言而喻。

为什么STM32要有多个时钟源呢?

STM32本身十分复杂,外设非常多 但我们实际使用的时候只会用到有限的几个外设,使用任何外设都需要时钟才能启动,但并不是所有的外设都需要系统时钟那么高的频率,为了兼容不同速度的设备,有些高速,有些低速,如果都用高速时钟,势必造成浪费 并且,同一个电路,时钟越快功耗越快,同时抗电磁干扰能力也就越弱,所以较为复杂的MCU都是采用多时钟源的方法来解决这些问题。所以便有了STM32的时钟系统和时钟树。

总结:

-

STM32时钟系统主要的目的就是给相对独立的外设模块提供时钟,也是为了降低整个芯片的耗能。

-

系统时钟,是处理器运行时间基准(每一条机器指令一个时钟周期)

-

时钟是单片机运行的基础,时钟信号推动单片机内各个部分执行相应的指令。

-

一个单片机内提供多个不同的系统时钟,可以适应更多的应用场合。

-

不同的功能模块会有不同的时钟上限,因此提供不同的时钟,也能在一个单片机内放置更多的功能模块。对不同模块的时钟增加开启和关闭功能,可以降低单片机的功耗。

-

STM32为了低功耗,他将所有的外设时钟都设置为disable(不使能),用到什么外设,只要打开对应外设的时钟就可以, 其他的没用到的可以还是disable(不使能),这样耗能就会减少。 这就是为什么不管你配置什么功能都需要先打开对应的时钟的原因

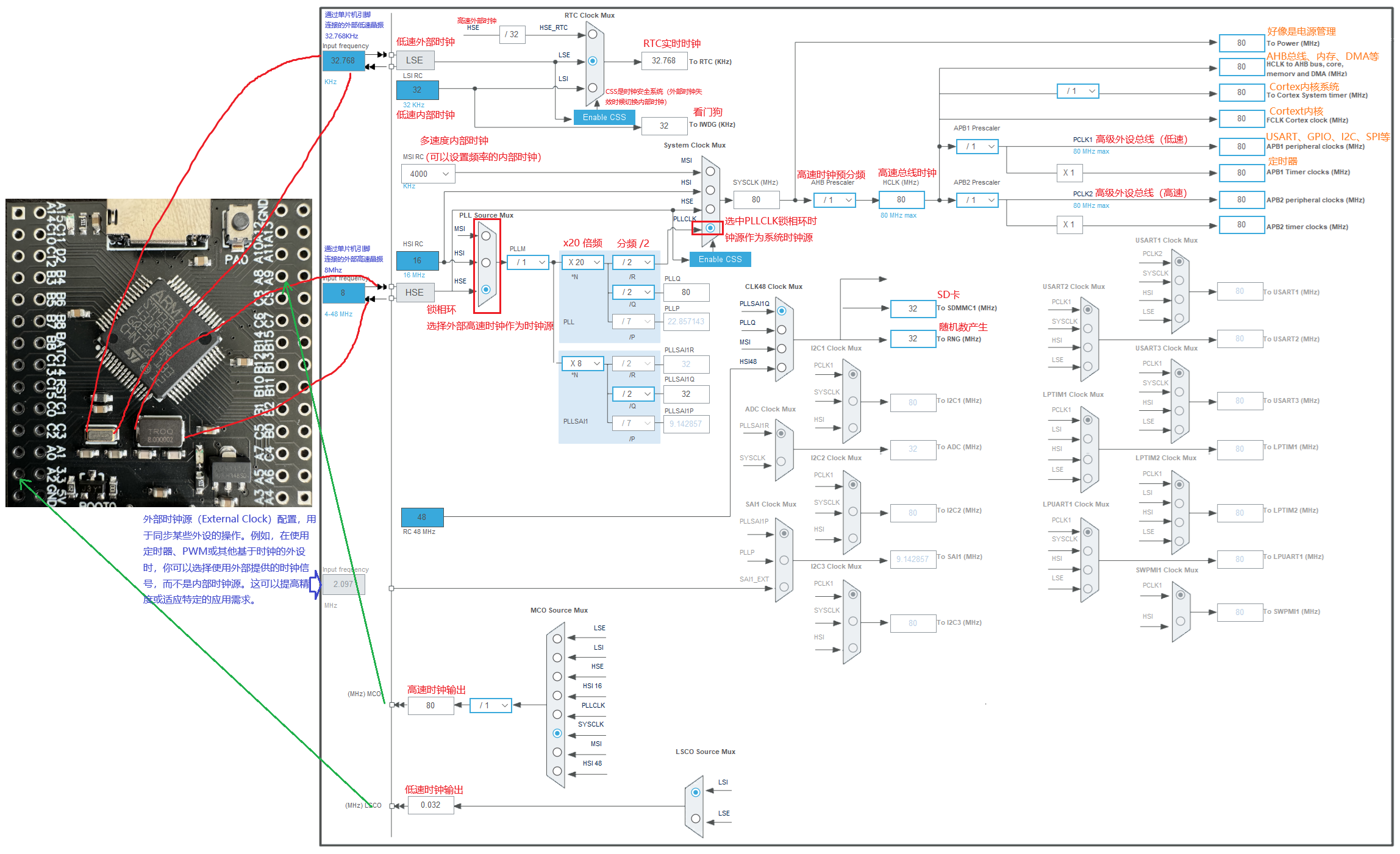

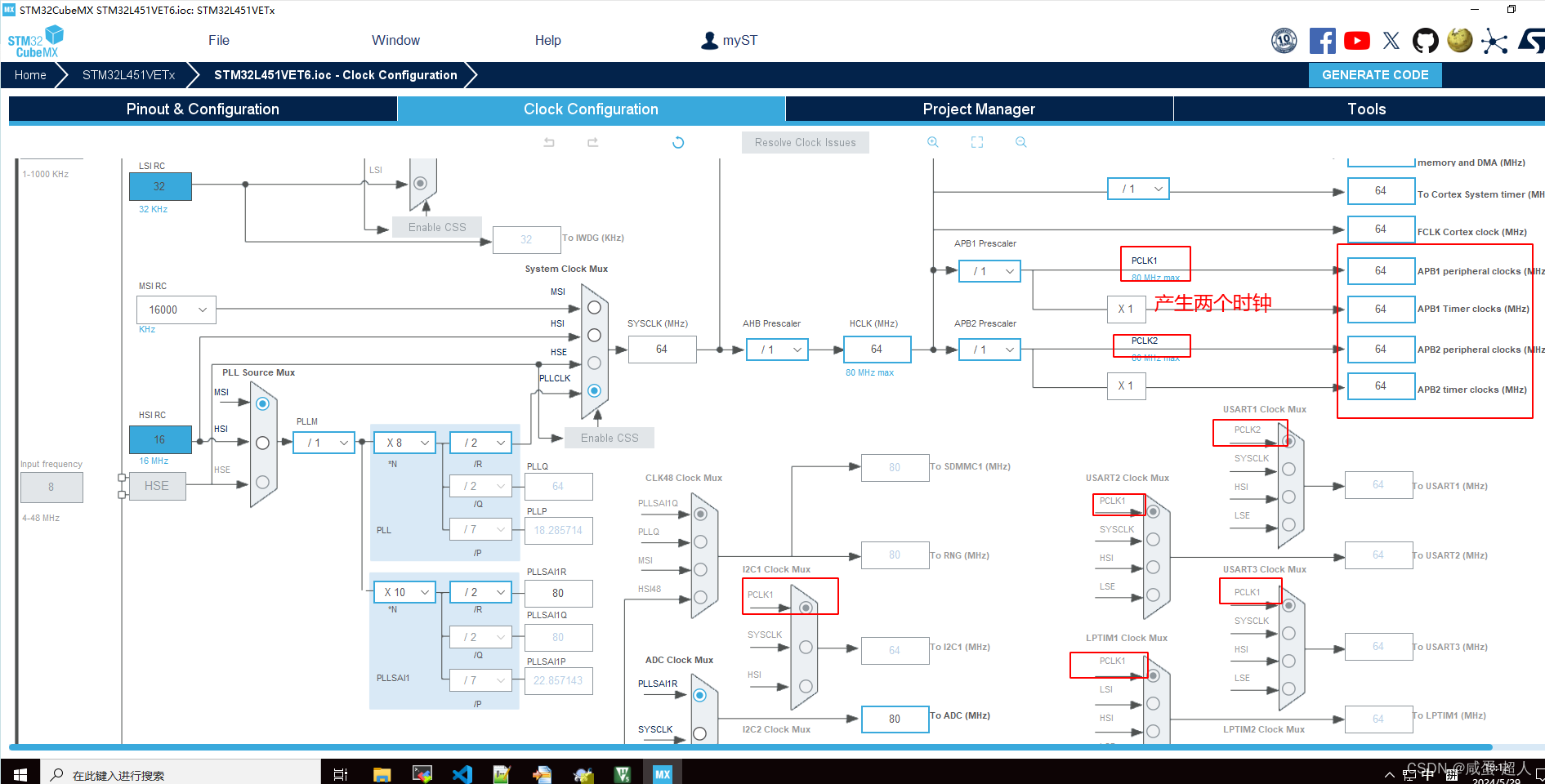

2 STM32时钟系统框图

2.1 输入时钟源

STM32L4X系列有五个个独立时钟源:HSI、HSE、LSI、LSE、MSI

-

LSI(Low-Speed Internal RC Oscillator):低速内部时钟,RC振荡器。

通常工作在几十Khz范围内,用于一些低功耗模式下的定时器、RTC时钟或者看门狗定时器功能。

-

HSI(High-Speed Internal RC Oscillator):高速内部时钟,RC振荡器

高速内部RC振荡器,通常工作在几十兆赫兹的频率范围内。HSI时钟是STM32微控制器的主要时钟源之一,用于驱动处理器核心和大部分外设模块的正常运行。

-

LSE(Low-Speed External):外部高速振荡器,可以连接到微控制器的晶体振荡器引脚(OSC_IN和OSC_OUT)。

外部时钟振荡器一般采用晶体振荡器,他可以提供更高的准确性和稳定性。 但是同时成本也更高一些

-

HSE(High-Speed External):一种用于提供低速时钟信号的外部时钟源。

STM32微控制器中,LSE通常指的是外部32.768kHz晶体振荡器,因为它的频率正好是2的15次方,可以很方便地与RTC的预分频器相结合,从而实现精确的秒级时间计数。

-

MSI(Multi-Speed Internal RC Oscillator):在STM32L4系列微控制器中引入的新型内部时钟源。

MSI时钟源提供了多个可选的频率档位,可以根据应用的需求选择不同的频率,从数百千赫兹到数十兆赫兹不等。

2.2 输出时钟源

输出时钟源可以给其他外部连接设备(不是单片机片内)提供时钟源。

通过 System Core 中的 RCC 可以设置使能时钟输出功能。

-

MCO(Master Clock Output):主要时钟输出(高速时钟输出)

-

LSCO(LSCO Clock Output):低速时钟输出

2.3 低速时钟作用

-

RTC(Real Time Clock):在单片机中的作用是提供精确的时间基准,并确保在掉电后时间信息的连续性。

-

IWDG(Independent Watchdog):独立看门狗,是一个关键的安全特性,旨在提高系统的可靠性和稳定性。

IWDG的主要作用是监控微控制器的运行状态,防止因软件错误、外部干扰或其他异常情况导致的系统停滞或死机。当系统正常运行时,IWDG会定期被软件重置(即“喂狗”)。如果系统因为某种原因停止正常工作,软件将无法及时重置IWDG,导致IWDG超时并触发系统复位,从而使系统恢复到初始状态,避免长时间的停滞或错误状态。

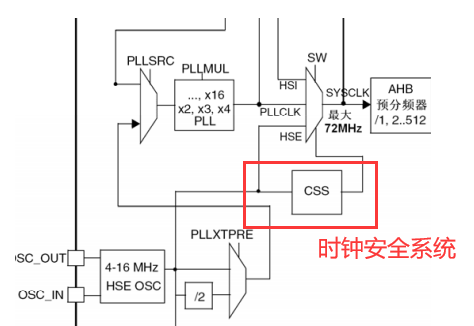

2.4 CSS

CSS(Clock Safe System):时钟安全系统。监视高速外部时钟HSE的工作状态。若HSE失效,会自动切换,会自动切换高速内部时钟HSI作为系统时钟的输入,保证系统的正常运行。一旦CSS被激活,并且HSE时钟出现故障,CSS中断就产生,并且NMI也自动产生。NMI将被不断执行,直到CSS中断挂起位被清除。

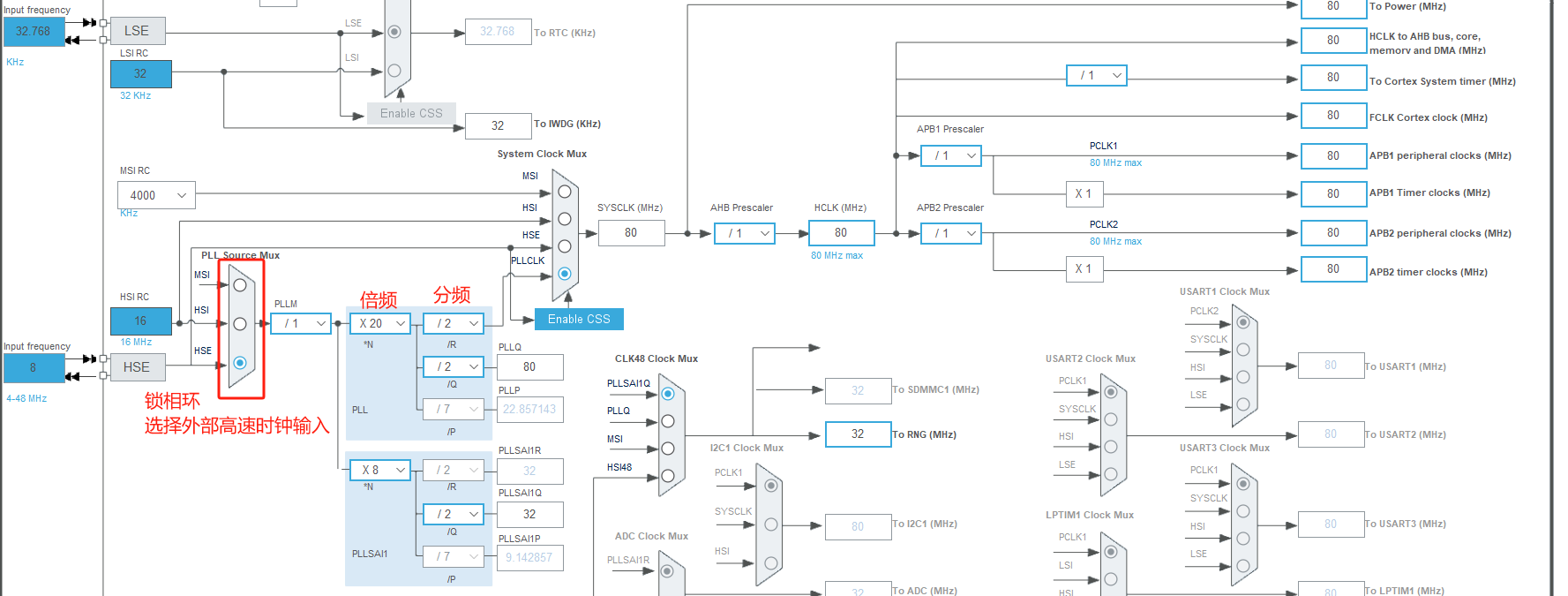

2.5 PLL Source Mux

PLL(phase locked loop)锁相环是一种电路,可根据输入的参考时钟信号生成一个高频率的时钟信号输出。(倍频作用)

2.6 SYSCLK

-

指在STM32微控制器中用于驱动整个系统(应该也可以说是CPU)的时钟信号。它是所有内部模块和外设的时钟源,对于系统的正常运行至关重要。

-

Sysclk的频率和稳定性直接影响着处理器的运行速度、外设的工作性能以及整个系统的功耗。

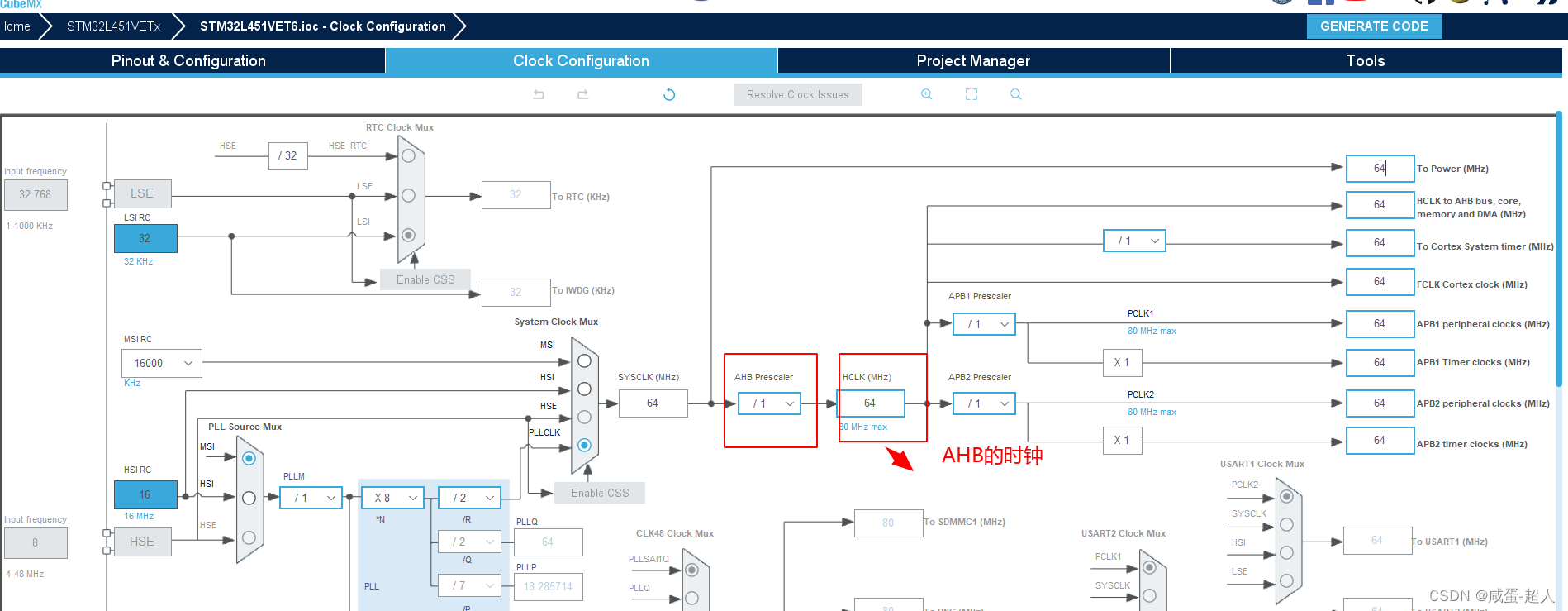

2.7 AHB和HCLK

AHB是什么?

AHB(Advanced High-performance Bus)是一种用于连接主要系统总线和高性能外设的总线架构,它是STM32微控制器中的主要系统总线之一,用于连接处理器核、内存和高带宽外设,如DMA控制器、高速存储器接口等

为什么会有AHB?

高性能需求:一些外设,比如DMA控制器、存储器接口等,需要更高的数据传输速度和带宽,而普通的总线无法满足这些要求。 分流系统负载:将外设的访问流量从主系统总线中分流出来,可以减轻主系统总线的负荷,提高整个系统的效率和性能。

AHB prescaler(AHB预分频器)

是用来设置Advanced High-performance Bus(AHB)时钟频率的寄存器。通过配置AHB预分频器,可以将系统时钟(SYSCLK)分频后得到AHB总线的工作频率。

HCLK(AHB Clock)

HCLK就是AHB 总线的时钟

2.8 APB和PCLK

-

APB:APB代表高级外设总线(Advanced Peripheral Bus),是连接外设的总线。在STM32微控制器中,通常有两种类型的APB总线:APB1和APB2。

-

APB1:APB1主要连接低速外设

-

APB2:APB2主要连接高速外设

-

PCLK:APB1上的时钟为PCLK1,APB2上的时钟为PCLK2

参考

时钟

https://blog.csdn.net/as480133937/article/details/98845509

https://blog.csdn.net/Wang2869902214/article/details/142423522

https://blog.csdn.net/weixin_74209413/article/details/138749590

https://www.eeworld.com.cn/mcu/hisic507546.html

滴答计时器

https://blog.csdn.net/qq_61984785/article/details/141267704

https://blog.csdn.net/yu132563/article/details/53414894

https://blog.csdn.net/xiaogu0322/article/details/78644302