二十、STM32——FSMC

1 FSMC的概念及结构框图

F7/H7具有MPU单元的单片机,操作外设地址总线。1.1 FSMC概念

FSMC,Flexible Static Memory Controller,灵活的静态存储控制器。

用于驱动SRAM,NOR FLASH,NAND FLASH及PC卡类型的存储器。配置好FSMC,定义一个指向这些地址的指针,通过对指针操作就可以直接修改存储单元的内容,FSMC自动完成读写命令和数据访问操作,不需要程序去实现时序。也就是无需手动去拉高、拉低信号实现选择写、读和选择读写命令、数据等东西。

F1/ F4(407)系列大容量型号,且引脚数目在100脚以上的芯片都有FSMC接口。F4/F7/H7系列就是FMC接口,区别是FMC可以直接驱动SDRAM,FSMC不行。

1.1.1 FSMC(Flexible Static Memory Controller)

-

FSMC主要用于控制静态存储器,如SRAM(Static Random Access Memory)等。不能扩展SDRAM。

-

FSMC提供了与静态存储器进行接口通信的功能,包括读取和写入数据,控制地址线和数据线的操作等。

-

FSMC通常用于需要快速访问速度和低延迟的应用场景,例如高性能嵌入式系统中。

1.1.2 FMC(Flexible Memory Controller)

-

FMC则更加灵活,可以用于控制各种类型的存储器,包括SDRAM(Synchronous Dynamic Random Access Memory)、NOR Flash、NAND Flash等。

-

FMC支持更多种类的存储器接口标准和协议,使其在连接各种存储器时更具通用性和灵活性。

-

FMC通常用于需要较大存储容量或者对存储器种类要求较多样化的系统中。

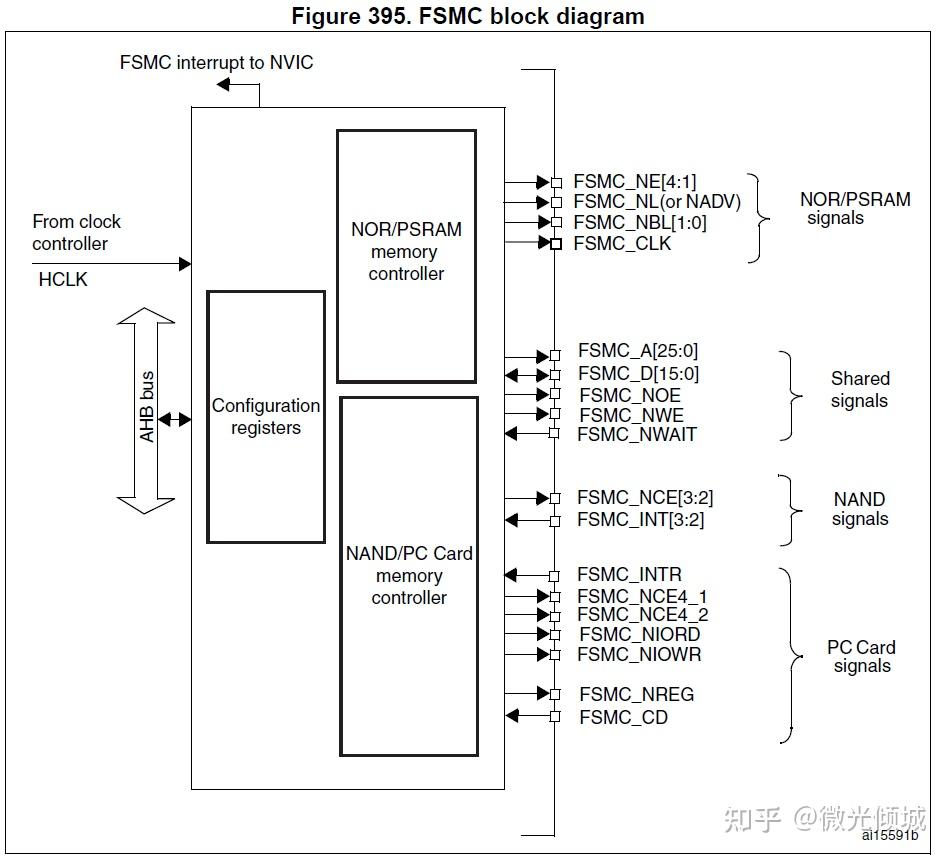

2 FSMC接口

所有的外部存储器共享这几种接口:地址总线(FSMC_A[25:0])、数据总线(FSMC_D[15:0])和控制信号(FSMC_NOE、FSMC_NWE、FSMC_NWAIT)。比如我同时有SRAM和NAND Flash,他们两个的地址、数据、控制信号GPIO口是连接到一起的。他们通过各自的片选接口,选择跟那个芯片通信。FMC将外部设备分为以下三类:

-

NOR/PSRAM/SRAM/ROM/LCD: 这类型设备使用相同的控制器。

-

NAND Flash:是一类设备。

-

SDRAM:是一类设备。TFTLCD可以当成SDRAM类型设备。

2.1 所有存储控制器公用引脚

-

FSMC_A[25:0]:地址总线

-

FSMC_D[15:0]:数据总线

-

FSMC_NOE:读使能

-

FSMC_NWE:写入使能

-

FSMC_NWAIT:该引脚作用是同步外部存储器的等待信号,当外部存储器(如 SRAM 或 NOR Flash)响应较慢时,它可以通过 NWAIT 引脚向 STM32 发送等待信号,以延长 FSMC 访问周期,避免访问错误。

2.2 NOR/PSRAM/SRAM/ROM/LCD

-

FSMC_NE[4:1] :不同的NE脚是控制不同的地址的,当STM32访问某个地址的时候,对应的NE引脚会被自动控制设成低电平,此时由于一个NE引脚连接到一个SRAM的CE引脚,所以SRAM的片选被使能。连接的就是外设芯片的CS引脚

-

FSMC_NL(or NADV) :对于 SRAM、NOR Flash 或 NAND Flash,此引脚通常不会用到。在 PC卡模式 下,FSMC_NL 作为 ADV#(地址有效信号),用于锁存地址信息。

-

FSMC_NBL[1:0] :FSMC_NBL0 控制低字节(D7-D0),FSMC_NBL1 控制高字节(D15-D8)。

-

FSMC_CLK :提供同步时钟信号,用于时序控制。

2.3 NAND/PC Card

这部分等使用的时候再补充

2.4 SDRAM

这部分等使用的时候再补充

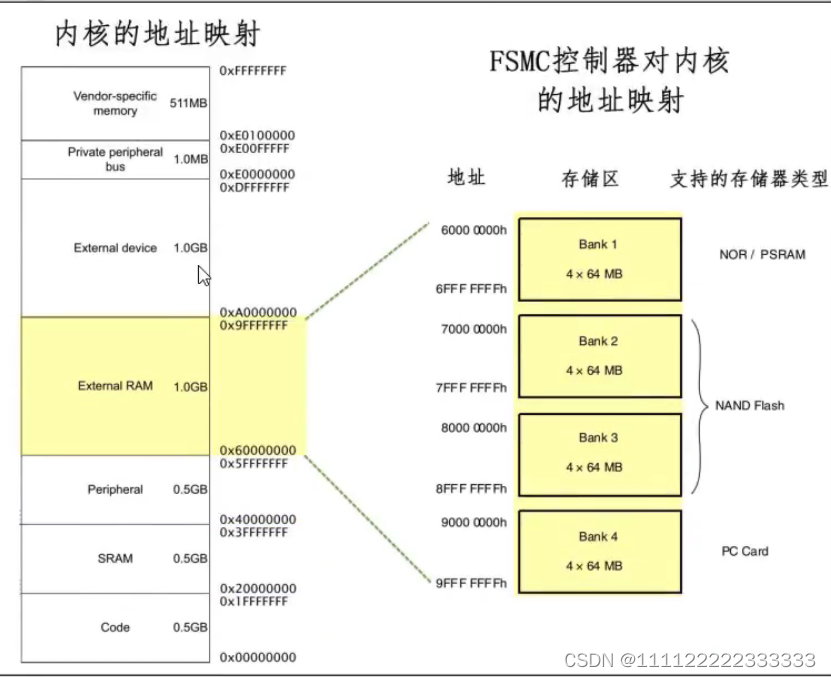

3 FSMC的地址映射

FSMC连接好外部的存储器并初始化后,就可以直接通过访问地址(C语言指针)来读写数据。

使用FSMC外接存储器时,其存储单元是映射到STM32的内部寻址空间的;在程序里,定义一个指向这些地址的指针,然后就可以通过指针直接修改该存储单元的内容,FSMC外设会自动完成数据访问过程,读写命令之类的操作不需要程序控制。

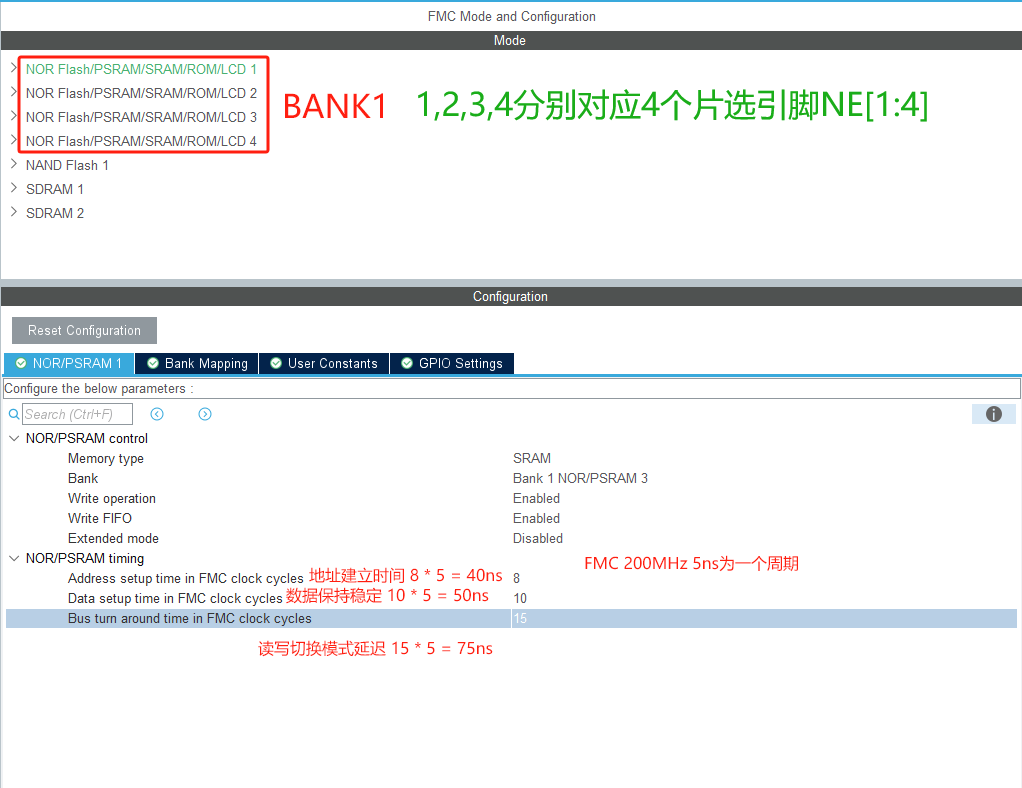

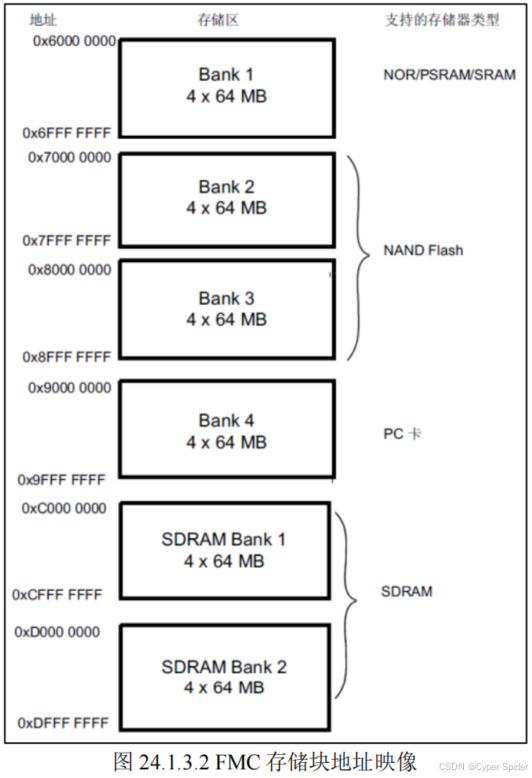

下面第一张图片是 FSMC 控制器对应内核地址映射,下面第二张图片是 FMC 存储块地址映射。每个Bank是256MB。

在 NOR/PSRAM/SRAM 区域,Bank1的内部又被分割成了4个小块,每个小块有相应的控制引脚 FSMC_NE 控制。当STM32访问0x68000000-0x6BFFFFFF地址空间时,会访问到Bank1的第3小块区域,相应的FSMC_NE3信号线会输出控制信号。

4 FMC四种时序

我DM9000外设使用的是模式A,好像设不设置时序,都不会影响设备正常工作。FMC 支持以下四种时序模式:

#define FMC_ACCESS_MODE_A ((uint32_t)0x00000000U)

#define FMC_ACCESS_MODE_B ((uint32_t)0x10000000U)

#define FMC_ACCESS_MODE_C ((uint32_t)0x20000000U)

#define FMC_ACCESS_MODE_D ((uint32_t)0x30000000)

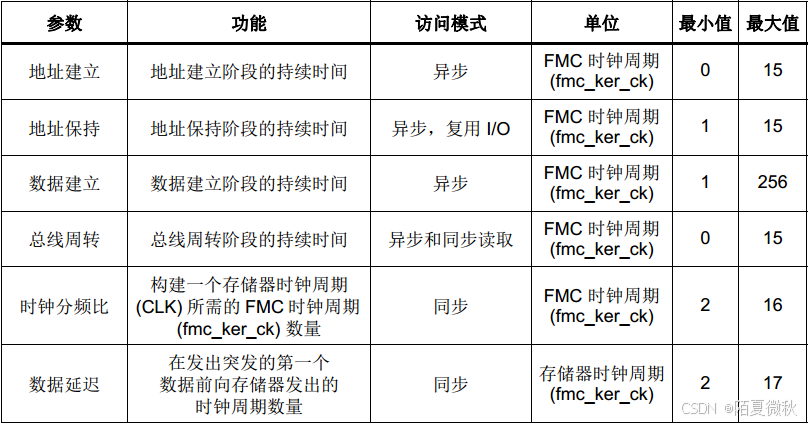

每个模式的时序略有不同,我们这里以常用的模式 A 为例进行说明:

-

AddressSetupTime:这个参数定义地址建立时间,即地址信号有效到读写使能开始之间的HCLK周期数。需要说明它用于确保地址信号在操作开始前稳定,适用于异步存储器如SRAM和异步NOR Flash,但不用于同步NOR Flash。可能需要注意不同存储器类型的差异。

-

AddressHoldTime:地址保持时间,地址信号在读写使能结束后继续保持的时间。同样适用于异步存储器,确保地址在操作结束后仍稳定一段时间,防止信号提前变化导致错误。需要提到其取值范围和适用情况。

-

DataSetupTime:数据建立时间,数据信号在写操作中保持稳定的时间,或者在读操作中等待数据准备好的时间。这个参数对于数据捕获的准确性至关重要,尤其是异步存储器。注意其取值范围较大,适用于SRAM、ROM和异步NOR Flash。

-

BusTurnAroundDuration:总线周转时间,用于切换读写模式时的延迟,防止总线冲突。主要针对复用总线的NOR Flash,避免读写切换时的信号冲突。需要解释总线周转的概念以及为何需要这个参数。

-

CLKDivision:时钟分频,定义CLK输出信号的周期,适用于同步存储器如SDRAM或同步NOR Flash。分频系数决定了存储器的时钟频率,需平衡速度和稳定性,注意它不用于异步存储器。

-

DataLatency:数据延迟,在同步突发模式下,从发出读命令到第一个数据到达所需的时钟周期数。这个参数需要根据存储器规格设置,例如SDRAM的行地址到列地址延迟(CL)。注意不同存储器的应用场景,如CRAM需设为0,异步存储器则不关心。

模式A用不到 AddressHoldTime、CLKDivision、DataLatency 参数

FMC 的 SRAM/NOR FLASH 控制器支持 同步突发访问 和 异步突发访问 两种方式。

-

同步突发访问:FMC 将 系统时钟HCLK 分频后,发送给外部存储器作为 同步时钟信号FMC_CLK。此时需要设置的时间参数有时钟分频系数(CLKDivision)、获取第1个数据所需要的等待延迟(DataLatency)。

-

异步突发访问:FMC 主要设置 3 个时间参数:地址建立时间(AddressSetupTime)、数据建立时间(DataSetupTime) 和 地址保持时间(AddressHoldTime)。

FMC综合了 SRAM、PSRAM和 NOR Flash 产品的信号特点,定义了 4 种不同的异步时序模型。选用不同的时序模型时,需要设置不同的时序参数。

5 CubeMX配置FSMC